# ECE241 – Digital Systems Finite State Machines (review)

Fall 2023 – Bruno Korst, P.Eng.

1

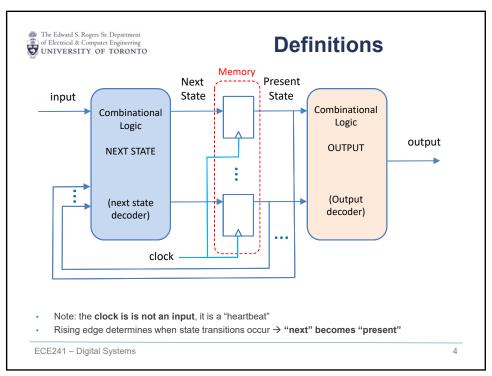

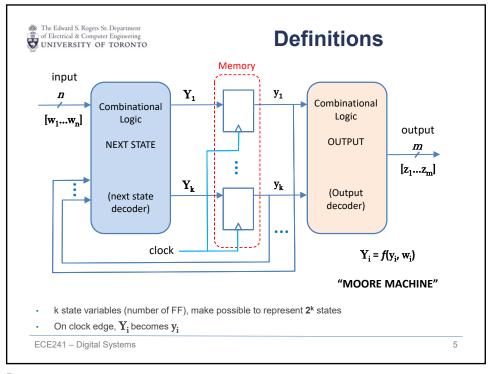

#### **Definitions**

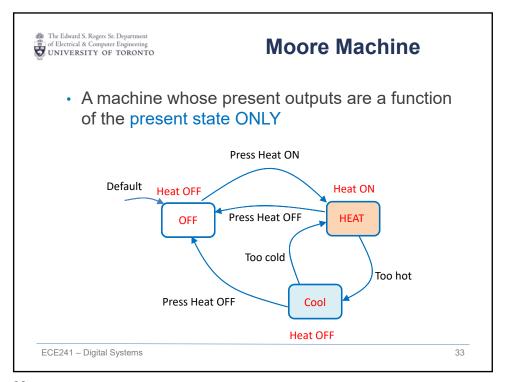

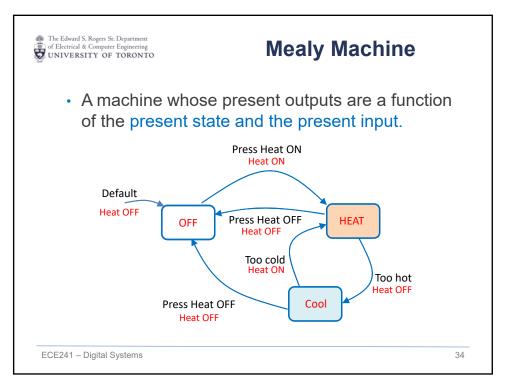

- Synchronous Sequential Machine

- Machine whose present outputs are a function of the present state

OR

- Machine whose present outputs are a function of the present inputs and the present state.

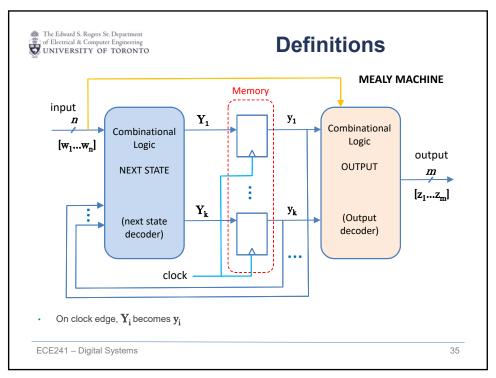

- Synchronous → "responds to a clock"

- Sequential logic system → combinational logic + storage

ECE241 - Digital Systems

2

#### **Definitions**

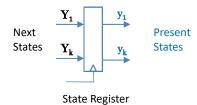

- State is "a set of values that is measured at different locations within the machine" (stored, in clocked D-FF, registers)

- Present state: state of the system at the present

- Next state: state to which the system will enter on the next clock edge.

ECE241 - Digital Systems

3

3

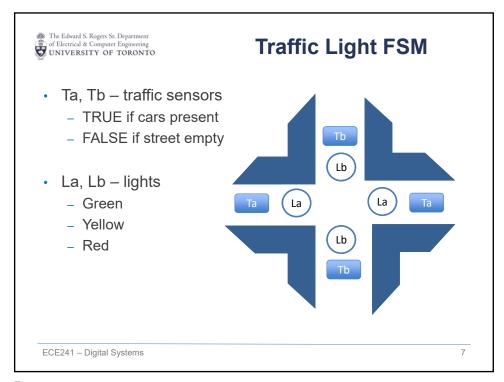

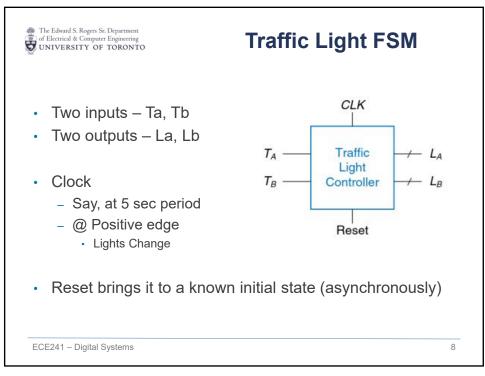

## **Traffic Light FSM**

#### The problem

- There is an intersection of two busy roads which needs traffic lights to prevent collisions.

- These lights are to be controlled by traffic sensors, which indicate whether there are cars present or not.

ECE241 - Digital Systems

6

- A systematic approach to the design

- 1. Draw the state transition diagram

- 2. Create the state transition table

- 3. Encode the states on the state transition table

- 4. Derive the logic expressions, minimize them

- 5. Create the output table, encode it

- 6. Derive the logic expressions, minimize them

- 7. Draw the circuit, implement it

- · On "old-school" hardware, in code, on HDL

ECE241 - Digital Systems

9

9

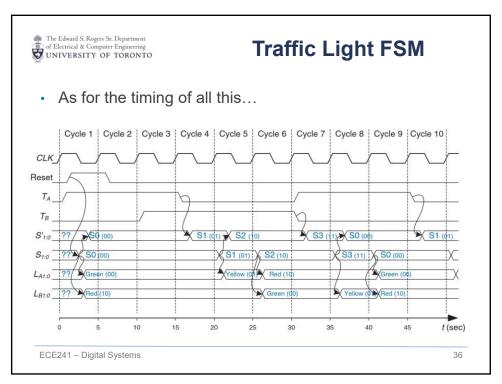

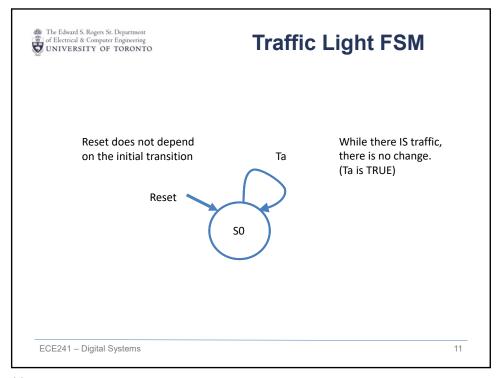

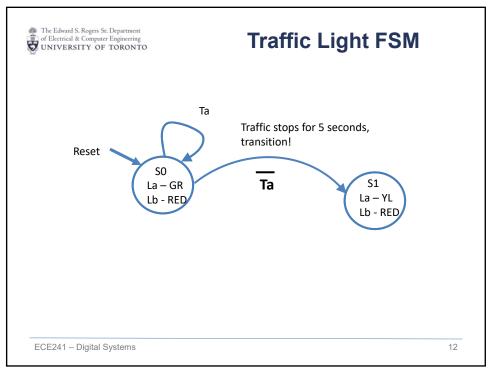

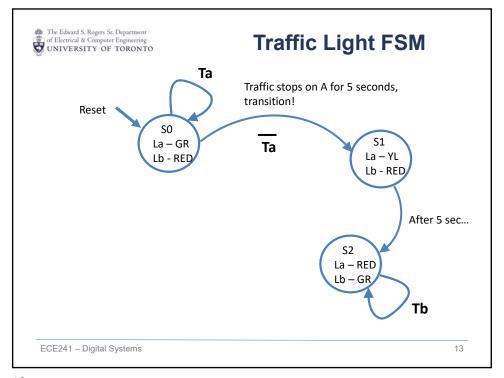

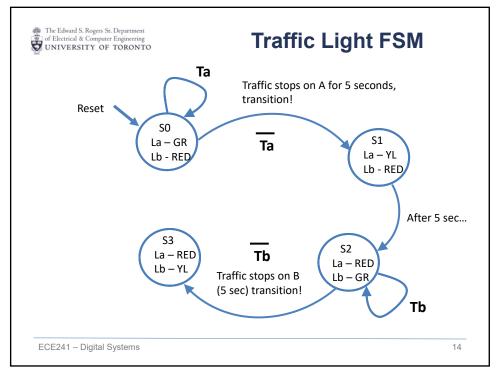

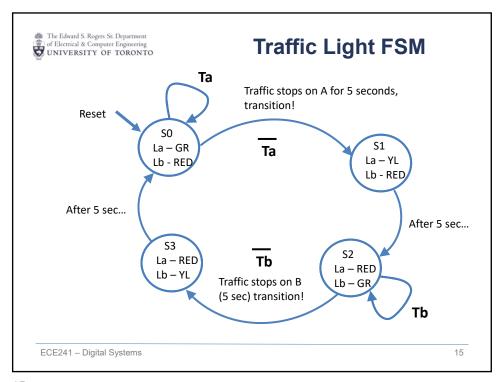

#### **Traffic Light FSM**

- State Transition Diagram

- States are represented by circles, transitions by arcs

- Reset green on "A" street, red on "B" street

- Every 5 seconds (clock), examine sensors (Ta, Tb) and decide:

- Is traffic present on A if so, lights do not change

- · When no more traffic on A for 5 seconds light turns yellow on A

- · 5 seconds later, red on A, green on B

ECE241 - Digital Systems

10

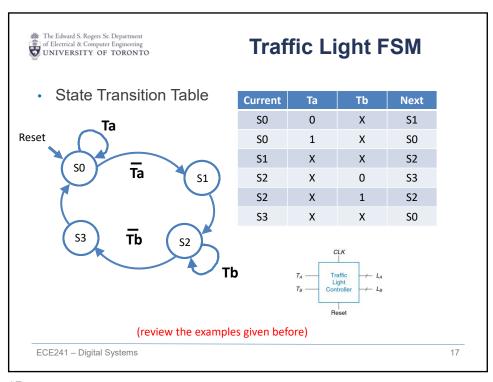

## **Traffic Light FSM**

- · A systematic approach to the design

- 1. Draw the state transition diagram

- 2. Create the state transition table

- 3. Encode the states on the state transition table

- 4. Derive the logic expressions, minimize them

- 5. Create the output table, encode it

- 6. Derive the logic expressions, minimize them

- 7. Draw the circuit, implement it

- · On "old-school" hardware, in code, on HDL

ECE241 - Digital Systems

16

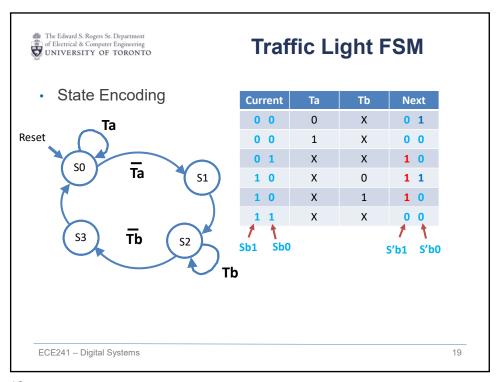

## **Traffic Light FSM**

- · A systematic approach to the design

- 1. Draw the state transition diagram

- 2. Create the state transition table

- 3. Encode the states on the state transition table

- 4. Derive the logic expressions, minimize them

- 5. Create the output table, encode it

- 6. Derive the logic expressions, minimize them

- 7. Draw the circuit, implement it

- · On "old-school" hardware, in code, on HDL

ECE241 - Digital Systems

18

## **Traffic Light FSM**

- · A systematic approach to the design

- 1. Draw the state transition diagram

- 2. Create the state transition table

- 3. Encode the states on the state transition table

- 4. Derive the logic expressions, minimize them

- 5. Create the output table, encode it

- 6. Derive the logic expressions, minimize them

- 7. Draw the circuit, implement it

- · On "old-school" hardware, in code, on HDL

ECE241 - Digital Systems

20

Logic Expressions

| Current | Та | Tb | Ne        | ext  |

|---------|----|----|-----------|------|

| 0 0     | 0  | Χ  | 0         | 1    |

| 0 0     | 1  | Χ  | 0         | 0    |

| 0 1     | X  | Χ  | 1         | 0    |

| 1 0     | Χ  | 0  | 1         | 1    |

| 1 0     | X  | 1  | 1         | 0    |

| 1 1     | X  | X  | 0         | 0    |

| Sb1 Sb0 | )  | 9  | /<br>5'b1 | S'b0 |

$$\begin{aligned} \mathbf{S'b_1} &= \overline{Sb_1}Sb_0 + Sb_1\overline{Sb_0}\,\overline{T_b} + Sb_1\overline{Sb_0}T_b \\ \mathbf{S'b_0} &= \overline{Sb_1}\,\overline{Sb_0}\,\overline{T_a} + Sb_1\overline{Sb_0}\,\overline{T_b} \end{aligned}$$

ECE241 - Digital Systems

21

21

### **Traffic Light FSM**

Logic Expressions

| Current | Та | Tb | Next |

|---------|----|----|------|

| 0 0     | 0  | Χ  | 0 1  |

| 0 0     | 1  | Χ  | 0 0  |

| 0 1     | Х  | Х  | 1 0  |

| 1 0     | Х  | 0  | 1 1  |

| 1 0     | Χ  | 1  | 10   |

| 1 1     | Χ  | Χ  | 0 0  |

| Sb1 Sb0 | )  | :  | /    |

$$S'b_{1} = \overline{Sb_{1}}Sb_{0} + Sb_{1}\overline{Sb_{0}}\overline{T_{b}} + Sb_{1}\overline{Sb_{0}}\overline{T_{b}}$$

$$S'b_{0} = \overline{Sb_{1}}\overline{Sb_{0}}\overline{T_{a}} + Sb_{1}\overline{Sb_{0}}\overline{T_{b}}$$

ECE241 - Digital Systems

22

• State Transition Table – next states from current states

| Current | Та | Tb | Next |            |

|---------|----|----|------|------------|

| 0 0     | 0  | X  | 0 1  |            |

| 0 0     | 1  | Χ  | 0 0  |            |

| 0 1     | Х  | X  | 1 0  |            |

| 1 0     | Х  | 0  | 1 1  |            |

| 1 0     | Х  | 1  | 1 0  |            |

| 1 1     | Х  | Х  | 0 0  |            |

| 1 1     |    |    | 1 1  |            |

| Sb1 Sb0 |    | 9  | 5'b1 | <b>0</b> 0 |

$$S'b_1 = \overline{Sb_1}Sb_0 + Sb_1\overline{Sb_0}$$

$$S'b_0 = \overline{Sb_1}\overline{Sb_0}\overline{T_a} + Sb_1\overline{Sb_0}\overline{T_b}$$

$$\mathbf{S'b_1} = \mathbf{Sb_1} \oplus \mathbf{Sb_0}$$

$$S'b_0 = \overline{Sb_1} \, \overline{Sb_0} \, \overline{T_a} + Sb_1 \overline{Sb_0} \, \overline{T_b}$$

ECE241 - Digital Systems

23

23

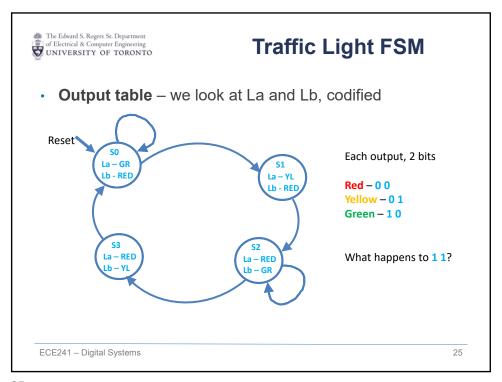

### **Traffic Light FSM**

- · A systematic approach to the design

- 1. Draw the state transition diagram

- 2. Create the state transition table

- 3. Encode the states on the state transition table

- 4. Derive the logic expressions, minimize them

- 5. Create the output table, encode it

- 6. Derive the logic expressions, minimize them

- 7. Draw the circuit, implement it

- · On "old-school" hardware, in code, on HDL

ECE241 - Digital Systems

24

- · A systematic approach to the design

- 1. Draw the state transition diagram

- 2. Create the state transition table

- 3. Encode the states on the state transition table

- 4. Derive the logic expressions, minimize them

- 5. Create the output table, encode it

- 6. Derive the logic expressions, minimize them

- 7. Draw the circuit, implement it

- · On "old-school" hardware, in code, on HDL

ECE241 - Digital Systems

27

27

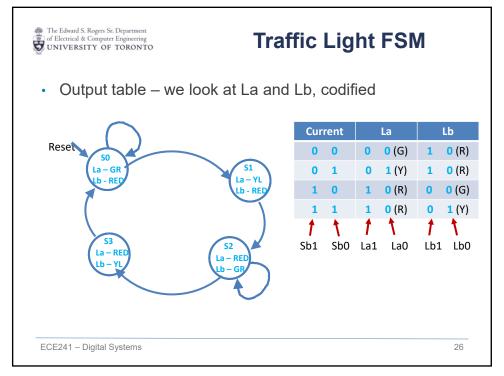

### **Traffic Light FSM**

· Output table – we look at La and Lb, codified

| Curi     | rent |     | La           |          | Lb    |

|----------|------|-----|--------------|----------|-------|

| 0        | 0    | 0   | <b>0</b> (G) | 1        | 0 (R) |

| 0        | 1    | 0   | 1 (Y)        | 1        | 0 (R) |

| 1        | 0    | 1   | 0 (R)        | 0        | 0 (G) |

| 1        | 1    | 1   | 0 (R)        | 0        | 1 (Y) |

| <i>†</i> | 1    | t   | 1            | <b>†</b> | 1     |

| Sb1      | Sb0  | La1 | La0          | Lb1      | Lb0   |

$$La_{1} = Sb_{1}$$

$$La_{0} = \overline{Sb_{1}}Sb_{0}$$

$$Lb_{1} = \overline{Sb_{1}}$$

$$Lb_{0} = S_{1}S_{0}$$

ECE241 - Digital Systems

28

- · A systematic approach to the design

- 1. Draw the state transition diagram

- 2. Create the state transition table

- 3. Encode the states on the state transition table

- 4. Derive the logic expressions, minimize them

- 5. Create the output table, encode it

- 6. Derive the logic expressions, minimize them

- 7. Draw the circuit, implement it

- · On "old-school" hardware, in code, on HDL

ECE241 - Digital Systems

29

29

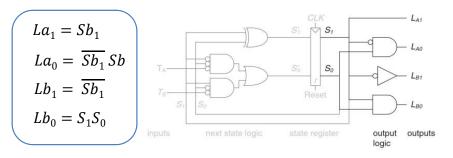

### **Traffic Light FSM**

· We've got equations for next states from current states

A 2 bit state register...

$$S'b_1 = Sb_1 \oplus Sb_0$$

$$S'b_0 = \overline{Sb_1} \overline{Sb_0} \overline{T_a} + Sb_1 \overline{Sb_0} \overline{T_b}$$

$$T_A = Sb_1 \otimes Sb_0 \otimes S$$

But that does not say anything about the output...

ECE241 - Digital Systems

30

S1

So

· We've ALSO got equations for outputs, which result in...

Note: Outputs depend only on the present state → MOORE MACHINE

ECE241 - Digital Systems

31

31

### **Traffic Light FSM**

ECE241 - Digital Systems

32